Indice

FET

I transistor ad effetto di campo

I transistor ad effetto di campo (field effect transistor) sono chiamati così perché sono comandati in tensione (invece che in corrente come i BJT). Sviluppati successivamente ai BJT erano inizialmente componenti meno veloci e affidabili; oggi sono usati moltissimo:

- negli integrati digitali, dove l'impiego dei MOSFET permette di ottenere soluzioni economiche ad elevata integrazione e basso consumo

- negli stadi di ingresso degli operazionali, dove i JFET permettono di ottenere una resistenza di ingresso molto elevata

- in forma discreta nell'elettronica di potenza, sia come amplificatori che come dispositivi ON-OFF, per il basso consumo

Le due famiglie principali di transistor FET sono:

- i JFET (junction FET) a giunzione

- i MOSFET o MOS (metal-oxide-semiconductor FET) a metallo-ossido-semiconduttore, che possono essere di tipo enhancement e depletion

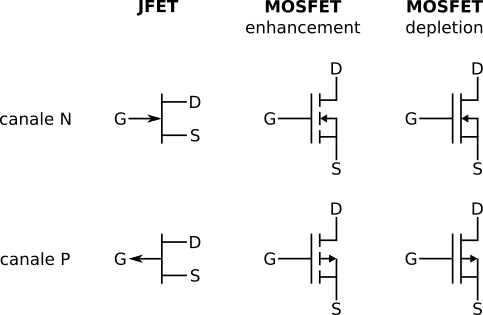

Come avviene per i BJT anche i FET sono disponibili in due varianti con portatori di carica di tipo diverso: quelli a canale N e quelli a canale P. Di seguito, per semplicità, faremo sempre riferimento ai FET a canale N.

I tre terminali dei transistor ad effetto di campo sono chiamati: source, drain e gate. Nei FET la corrente scorre in un canale fra i terminali di source e drain e il suo flusso è controllato dalla tensione applicata al terminale di gate.

La figura seguente mostra i simboli dei JFET, dei MOS enhancement e dei MOS depletion nelle due varianti a canale n e p1).

In tutti i casi vale sempre:

`I_D=I_S`

I JFET

I JFET sono meno usati rispetto ai MOSFET, con cui si realizzano gran parte dei dispositivi digitali, ma hanno delle caratteristiche che li rendono adatti per le applicazioni analogiche.

Struttura e funzionamento

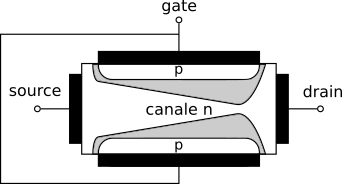

La figura seguente mostra la struttura di un JFET a canale n2).

Il transistor è composto da:

- una barra di semiconduttore di tipo n ai cui estremi sono posti gli elettrodi di source e drain

- due zone di tipo p collegate al gate

Fra gate è source è dunque presente una giunzione pn che, nel normale funzionamento del JFET, deve essere polarizzata inversamente (VGS ≤ 0).

Per comprendere il funzionamento del JFET supponiamo inizialmente che VGS sia zero. Se applichiamo una tensione VDS tra drain e source circolerà una corrente ID nel canale. Aumentando la VDS la corrente ID aumenta e il comportamento del JFET è resistivo. Tuttavia si verifica un altro fenomeno: nel canale si forma una zona di svuotamento (grigia in figura) dovuta alla polarizzazione inversa della giunzione, più pronunciata dal lato del drain e con un estensione crescente al crescere di VDS (gate e source sono allo stesso potenziale). La zona di svuotamento restringe il canale attraverso cui circola la ID e oltre una certa soglia di VDS si verifica lo strozzamento del canale (pinch-off) che impedisce alla corrente di aumentare; il JFET è in saturazione. Quando è presente una VGS (negativa) la zona di svuotamento si forma anche con VDS = 0 con la conseguenza che il JFET offre maggiore resistenza ed entra in saturazione prima.

Caratteristiche

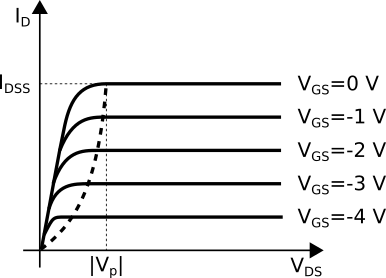

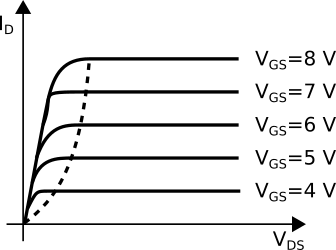

Osservando la caratteristica di uscita, che mostra la relazione tra la corrente ID e la tensione VDS per diversi valori di VGS, osserviamo che:

- è presente un'intera famiglia di caratteristiche dipendenti dal valore di VGS

- la saturazione del JFET, indicata dalla linea tratteggiata, avviene per valori via via minori di VDS all'aumentare (in modulo) di VGS

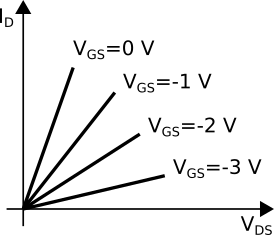

- a sinistra del tratteggio è presente una zona resistiva3) dove il JFET si comporta da resistenza variabile il cui valore dipende dalla tensione VGS (si veda la figura sotto che rappresenta un ingrandimento della caratteristica nell'origine)

- a destra di VP si trova la zona di saturazione a corrente costante dove il valore di ID dipende da VGS e non da VDS (NB nei BJT la saturazione è tutt'altra cosa!4) )

- per valori sufficientemente elevati di VGS lo strozzamento avviene già a VDS = 0 e non può circolare corrente; il JFET è interdetto

La relazione che permette di calcolare il valore della VDS alla quale avviene lo strozzamento è:

`V_(DS_(P))=V_P - V_(GS)`

Dove VP è la tensione di pinch-off quando VGS vale zero riportata nei data sheet.

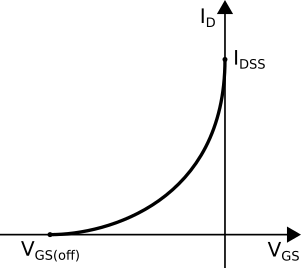

A questo punto è possibile osservare la caratteristica di trasferimento (figura sopra), valida per il funzionamento in saturazione, e osservare che:

- il JFET è interdetto se VGS è maggiore o uguale a VGS(off) = VP5)

- il massimo valore di corrente in condizione di saturazione si ha quando VGS vale zero ed è indicato con IDSS nelle due caratteristiche6)

- in corrispondenza di VGS = 0 e IDSS si ha la piena conduzione; in queste condizioni, se si opera nella zona resistiva, l'inverso della pendenza della caratteristica di uscita rappresenta la resistenza rDS(on) esibita dal JFET nello stato ON quando è usato in commutazione

Funzionamento in commutazione

Nell'impiego da amplificatori i JFET lavorano nella zona di saturazione, dove il comportamento è lineare; in quello in commutazione invece si lavora nella zona resistiva e in interdizione.

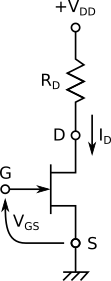

Il circuito in figura impone una retta di carico che dipende dall'alimentazione VDD e dalla resistenza RD collegate al drain. Il JFET lavorerà:

- in interdizione se VGS è negativa e maggiore di VGS(off)

- in piena conduzione (nella zona resistiva) se VGS è uguale a zero

I due punti di funzionamento si individuano incrociando la retta di carico con le caratteristiche di uscita del JFET corrispondenti ai due valori di VGS.

Funzionamento da amplificatore

I JFET possono essere impiegati anche come amplificatori. Come per i BJT occorre polarizzare correttamente il transistor, applicare un segnale e studiare la risposta dell'amplificatore con un circuito equivalente ai piccoli segnali.

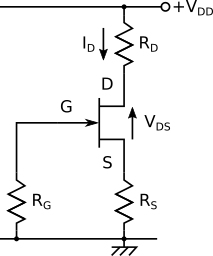

La figura sopra mostra il circuito di polarizzazione più semplice possibile dove:

- la resistenza RS tra source è massa è percorsa dalla corrente ID

- la resistenza RG collega a massa il gate ma non è percorsa da corrente

- la tensione VGS coincide in modulo con la caduta su RS

Studiando il circuito e conoscendo la relazione tra ID, RS e VGS è possibile imporre il punto di funzionamento a riposo.

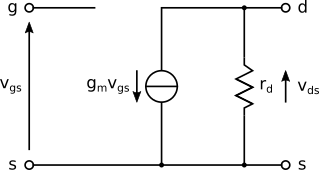

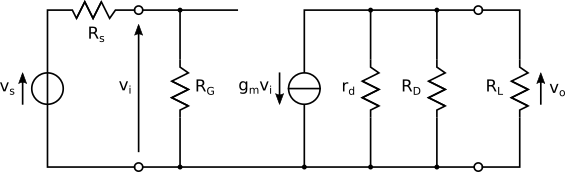

La figura seguente mostra il circuito equivalente ai piccoli segnali del JFET (si tratta di un circuito in centro banda a source comune simile a quello a emettitore comune dei BJT).

Osserviamo che:

- il gate è isolato

- il parametro principale è la transconduttanza `g_m = (i_d) / (v_(gs)) |_(v_(ds)=0)`

- il parametro rd è una resistenza differenziale che, in prima approssimazione, può essere considerata infinita (generatore di corrente ideale)

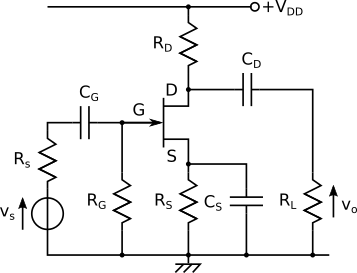

La configurazione completa di un amplificatore a source comune è quella mostrata in figura.

Riconosciamo il circuito di polarizzazione, la sorgente e il carico collegati tramite condensatori di bypass. Come per i BJT è possibile ricavare i parametri dell'amplificatore (guadagno, resistenze di ingresso e uscita) dal circuito equivalente ai piccoli segnali (figura sotto).

I MOSFET

I MOS sono i transistor più utilizzati nell'elettronica digitale perché permettono di realizzare integrati economici e a basso consumo. Sono impiegati anche nell'elettronica di potenza.

Per semplicità ci soffermeremo solo sui MOS ad arricchimento (enhancement), più semplici da capire e utilizzati nella tecnologia CMOS con cui si realizzano gli integrati digitali.

Struttura e funzionamento

La figura seguente mostra la struttura di un MOSFET enhancement a canale n, più brevemente chiamato NMOS7).

Il transistor è composto da:

- un substrato di tipo p collegato al source

- due zone di tipo n collegate ai terminali di source e drain

- uno strato di ossido di silicio (grigio scuro nel disegno) che isola il gate

In questo tipo di FET il gate è isolato e gli strati di materiali - metallo del terminale di gate, ossido e semiconduttore - danno il nome al componente.

Per comprendere il funzionamento del MOS supponiamo inizialmente che VGS valga zero. Applicando una tensione tra drain e source le due giunzioni substrato-source e substrato-drain non conducono e la ID è nulla (il substrato è collegato al source). Se ora applichiamo una tensione VGS positiva al gate il MOS si comporterà come un condensatore8) richiamando elettroni dalle tre zone e creando, oltre una soglia indicata con VGS(th), un canale di tipo n tra drain e source (grigio chiaro nel disegno). A questo punto, applicando una tensione VDS potrà circolare una corrente ID tra drain e source. Come per il JFET, per bassi valori di VDS il canale avrà un comportamento resistivo; per valori più elevati si avrà uno strozzamento dovuto al potenziale via via maggiore del terminale di drain che non permette alla corrente di aumentare. Aumentando il valore di VGS si ha un allargamento del canale e lo strozzamento avviene per valori di VDS più elevati.

Caratteristiche

In figura è rappresentata la caratteristica di uscita di un NMOS. La famiglia di curve che esprimono il legame tra ID e VDS è analoga a quella dei JFET ma la VGS è positiva e corrente e pendenza crescono al crescere di VGS. Anche in questo caso abbiamo una zona resistiva, a sinistra del tratteggio, e una di saturazione (attiva) a destra.

La figura sopra rappresenta la caratteristica di trasferimento, questa volta posta nel primo quadrante, dove compaiono:

- la tensione di soglia VGS(th) (indicata anche come VT) oltre la quale il MOS passa dall'interdizione alla conduzione

- la corrente IDSS, di valore trascurabile, che circola quando VGS vale zero

Nei data sheet è indicata anche una ID(on) che circola in in piena conduzione in corrispondenza di un determinato valore di VGS.

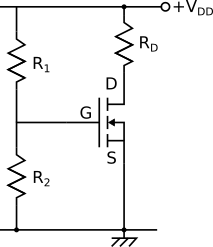

Diversamente dai JFET il transistor NMOS funziona con valori di VGS positivi; il circuito di polarizzazione sarà allora il seguente:

Nel funzionamento in commutazione si avrà:

- NMOS interdetto se VGS < VT

- NMOS in piena conduzione per valori sufficientemente alti di VGS

Il circuito per il funzionamento ON-OFF dell'NMOS è analogo a quello del JFET e per entrambi il comportamento del transistor può essere assimilato a quello di un interruttore con in serie una resistenza rDS(on) ricavabile dai data sheet9).

Navigazione

Torna all'indice.